### Avanergy: An Architecture-VLSI Abstraction for Automated Energy-Aware Design-Space Exploration Tools

### **Christopher Torng**

University of Southern California

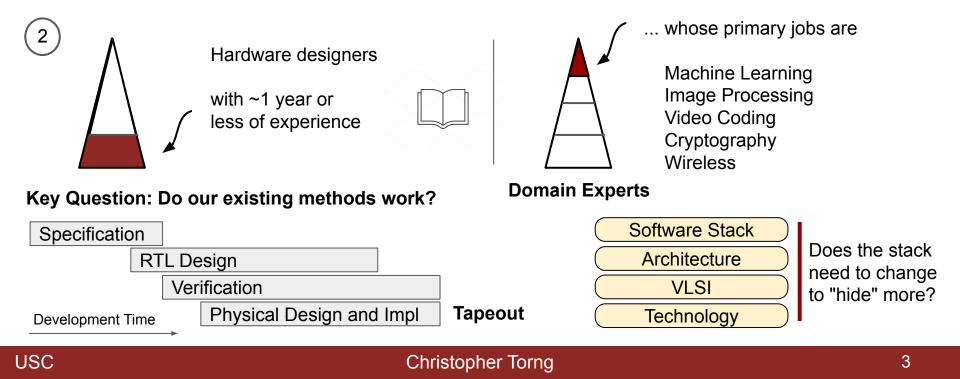

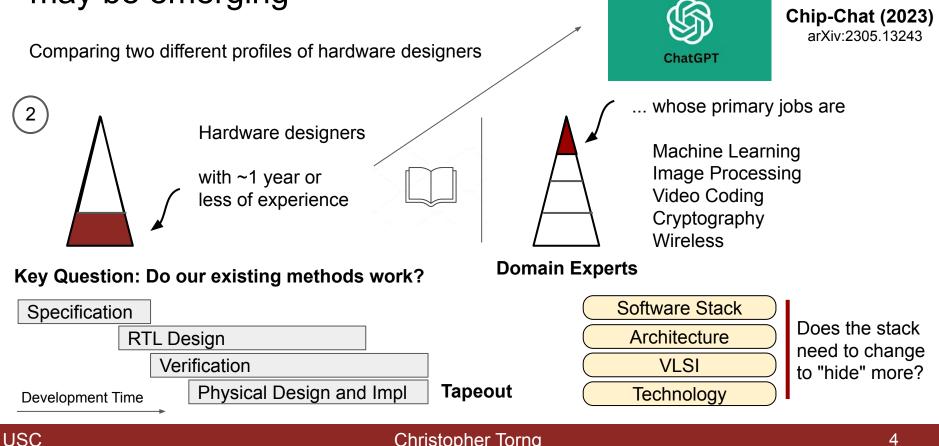

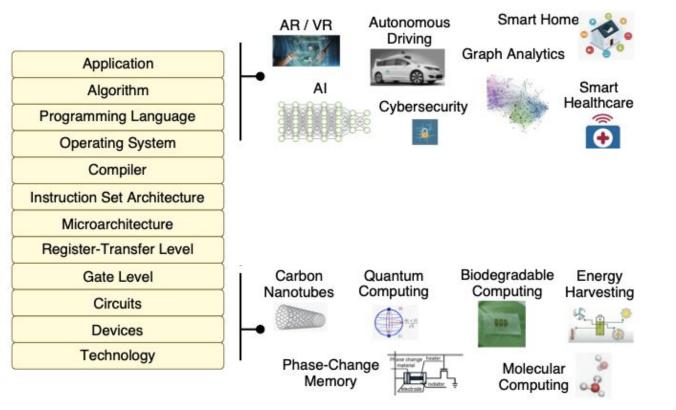

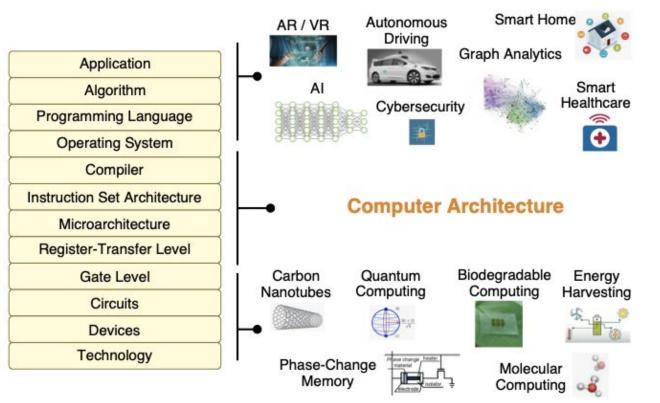

# A very different world of hardware design may be emerging

Comparing two different profiles of hardware designers

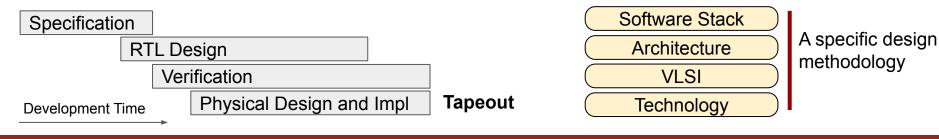

#### A specific way that things have always been done

# A very different world of hardware design may be emerging

Comparing two different profiles of hardware designers

### A very different world of hardware design may be emerging

## If properly empowered, this new audience could transform the hardware design community

#### Christopher Torng

## If properly empowered, this new audience could transform the hardware design community

#### Christopher Torng

## If properly empowered, this new audience could transform the hardware design community

### Quick Summary of New Audience

We may have more people ..

.. with less hardware expertise ..

.. who are relying heavily on automated tools

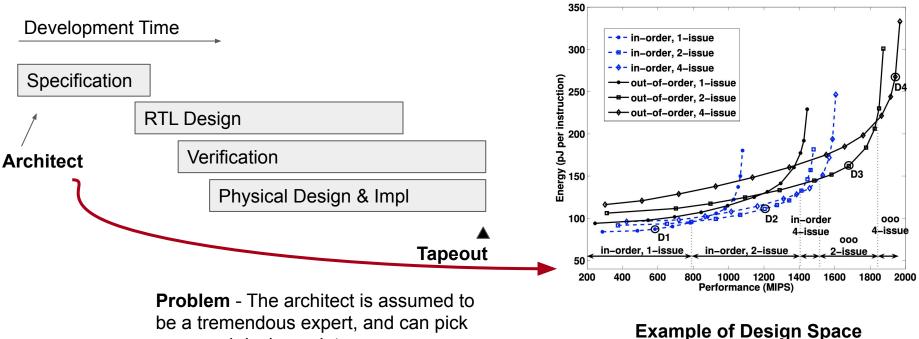

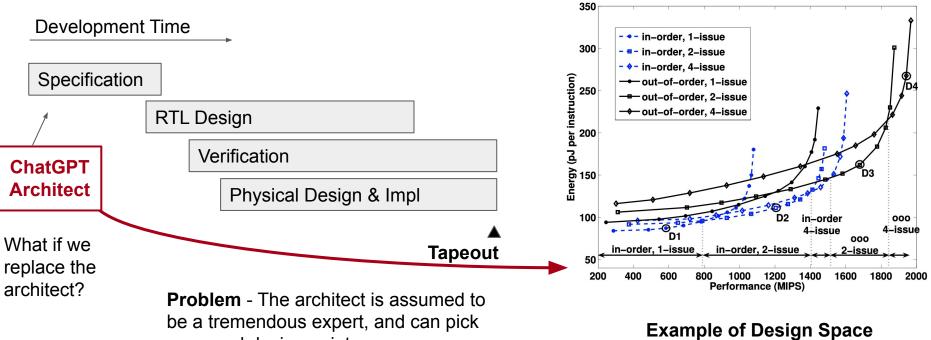

## Insight #1: Traditional design methodologies are built for our current profiles of expertise

#### Development Time

Specification

**RTL** Design

Verification

Physical Design & Impl

Tapeout

#### **Traditional Chip Development**

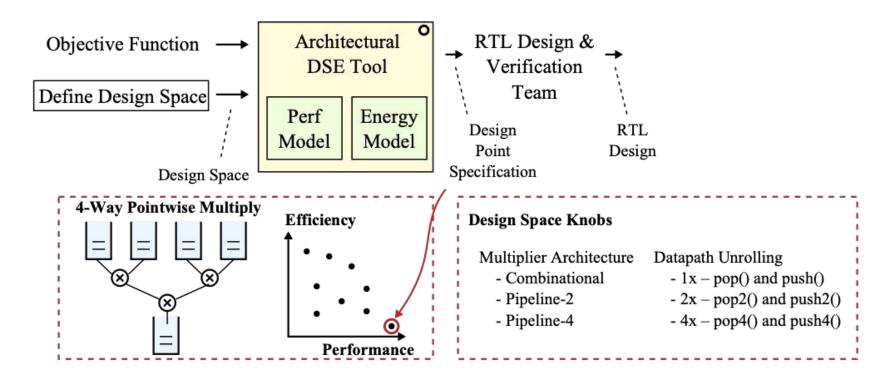

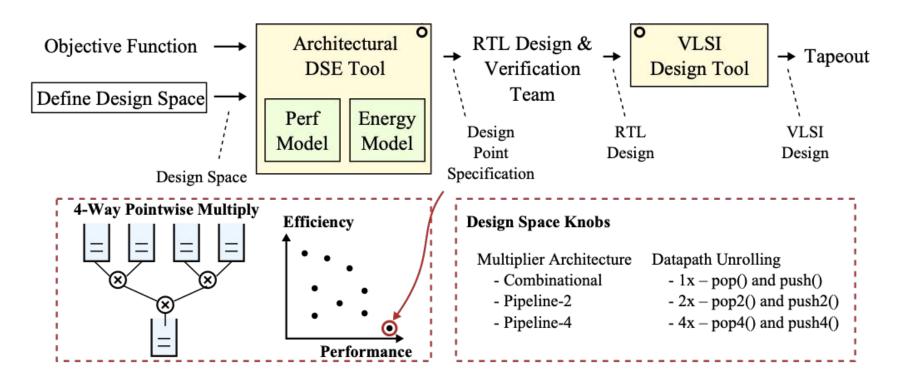

- An <u>architect</u> comes up with an architectural design specification

- The <u>RTL design team</u> takes the specification and builds the design

- In parallel, the <u>VLSI design team</u> moves through physical impl and iterates with RTL for refinement

- Tapeout

## Insight #1: Traditional design methodologies are built for our current profiles of expertise

one good design point among many ...

Azizi et al. (ISCA 2010)

## Insight #1: Traditional design methodologies are built for our current profiles of expertise

one good design point among many ...

Azizi et al. (ISCA 2010)

Insight #2: Iterative approaches can reduce the burden of getting things right the first time

- Multiple iterations leaves room to get it wrong and then correct the mistakes

- But the iterations must then become **very short** in order to fit multiple of them

- This exactly describes an agile hardware design methodology!

USC

|               | <b></b> |               |              |

|---------------|---------|---------------|--------------|

| Specification |         | Specification |              |

| RTL Design    |         | RTL Desig     | jn           |

| Verification  |         | Verific       | ation        |

| Physical      | Design  | Phy           | sical Design |

| Design Point  | #1      | Design        | Point #2     |

**Development Time**

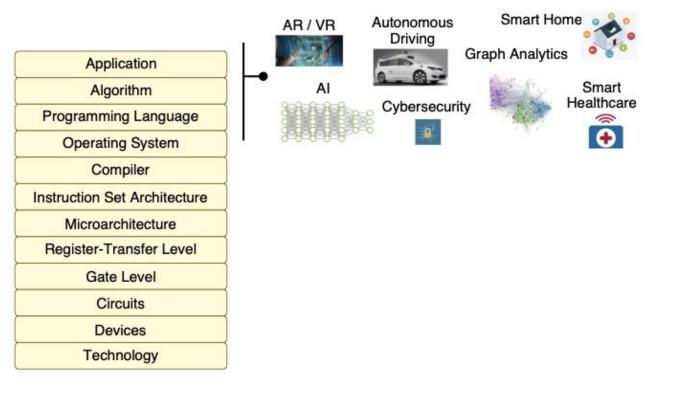

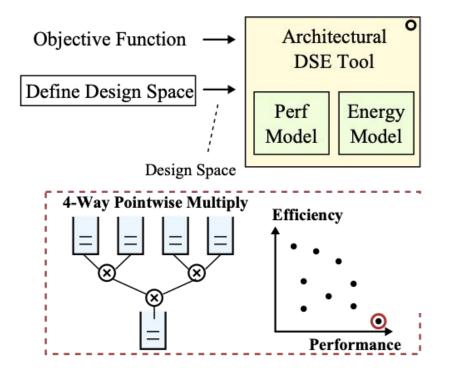

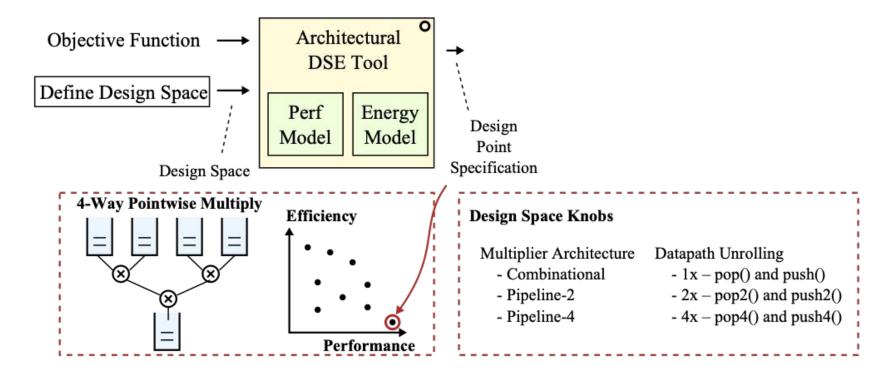

# Insight #3: Automation requires having systematic approaches built around quantifiable abstractions

Example question:

• How good of an energy efficiency result is good enough?

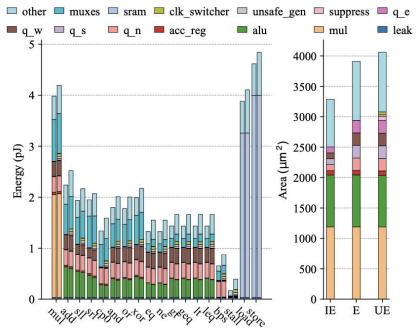

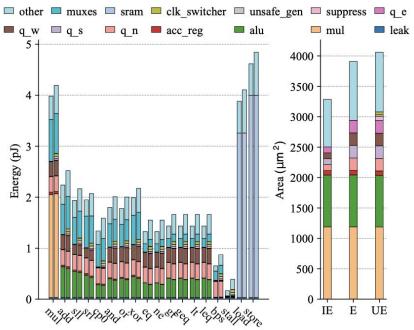

#### Example of Energy Breakdown Plot in 28nm Technology Torng et al. (HPCA 2021)

# Insight #3: Automation requires having systematic approaches built around quantifiable abstractions

Example question:

• How good of an energy efficiency result is good enough?

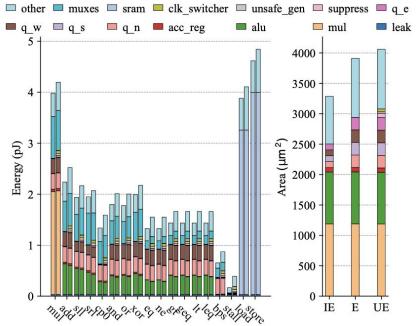

In an fully automated flow, there is no place for allowing designs to pass review that "look okay"

There must be a **quantifiable constraint**, as well as a systematic approach for generating these constraints and enforcing them.

Example of Energy Breakdown Plot in 28nm Technology Torng et al. (HPCA 2021)

# Insight #3: Automation requires having systematic approaches built around quantifiable abstractions

Example question:

How good of an energy efficiency result is good enough?

In an fully automated flow, there is no place for allowing designs to pass review that "look okay"

There must be a **quantifiable constraint**, as well as a systematic approach for generating these constraints and enforcing them.

Expert - Who will you hire to tell you it looks okay?

#### Example of Energy Breakdown Plot in 28nm Technology Torng et al. (HPCA 2021)

# Insight #4: Some aspects of complex SoC design pose a far more critical challenge than others

#### Case for Focusing on Energy

DSL-Based Accelerator PEak Program Lake Program Canal Program Generator (Interconnect Specification) (PE Specification) (MEM Specification) Integration Physical PEak PE Rewrite **MEM Rewrite** into SoC Lake Canal Routina Desian Compiler Compiler Compiler Graph Rules Rules SoC with CGRA RTL CGRA PE RTL MEM RTL Interconnect RTL Application Application Processor Code Compiler Schedulina Dataflow Dataflow > Mapper > Application with Halide Placer & Placement Bitstream CGRA Graph of > on CGRA in Halide Bitstream Compiler + Graph Router Generator PE/MEM Clockwork conv(x, y) += kernel(r.x, r.y) \*Μ x + Memory input(x+r.x, y+r.y); x + xconv.in().compute root(); conv.in() P P P + x .tile(x,y,xo,yo,xi,yi,64,64) + .hw accelerate(xi, xo); X х conv.update() + x + + .unroll(r.y, 3) .unroll(r.x, 3); +P)=PE conv.compute at(conv.in(), xo); XX input.stream to accelerator(); SR=Shift Register M=MEM C = Constant Example: 3x3 Convolution

Energy modeling is becoming more challenging at exactly the same time that automated approaches for energy are becoming increasingly valuable

- Scheduler Different kernel scheduling

- Compiler Different mappings

- Architecture Different compute and memory organization

- VLSI Ground truth

#### Christopher Torng

# Insight #4: Some aspects of complex SoC design pose a far more critical challenge than others

#### Case for Focusing on Energy

DSL-Based Accelerator PEak Program Lake Program Canal Program Generator (Interconnect Specification) (PE Specification) (MEM Specification) Integration Physical PEak PE Rewrite **MEM Rewrite** into SoC Lake Canal Routina Desian Compiler Compiler Compiler Graph Rules Rules SoC with CGRA RTL CGRA PE RTL MEM RTL Interconnect RTL Application Application Processor Code Compiler Scheduling Dataflow Dataflow > Mapper > Application with Halide Placer & Placement Bitstream CGRA Graph of > on CGRA in Halide Compiler + Bitstream Graph Router Generator PE/MEM Clockwork conv(x, y) += kernel(r.x, r.y) \*Μ x + Memory input(x+r.x, y+r.y); x + xconv.in().compute root(); conv.in() P P P + x .tile(x,y,xo,yo,xi,yi,64,64) + .hw accelerate(xi, xo); x х conv.update() + x + + .unroll(r.y, 3) .unroll(r.x, 3); P)=PE conv.compute at(conv.in(), xo); XX input.stream to accelerator(); SR=Shift Register M=MEM C = Constant Example: 3x3 Convolution

It is such a challenge that even experts do not want to do it

- TECS 2023

- TODAES 2022

- MICRO 2022

- IEEE MICRO 2020

- ICCAD 2019

Example - A series of very efficient academic CGRAs are marketed as"energy minimal", but they are in fact just "more efficient" than others

- MICRO 2022

- ISCA 2021

#### Christopher Torng

- How much should we refine an RTL design's energy efficiency to be "good enough"?

**Note #1**: Can you try to answer these questions as a hardware expert?

- How much should we refine an RTL design's energy efficiency to be "good enough"?

- Isn't lower energy always better?

**Note #1**: Can you try to answer these questions as a hardware expert?

- How much should we refine an RTL design's energy efficiency to be "good enough"?

- Isn't lower energy always better?

- What is a meaningful definition of an energy constraint?

**Note #1**: Can you try to answer these questions as a hardware expert?

**Note #2:** Notice that we also begin to introduce new terminology ... energy constraints

- How much should we refine an RTL design's energy efficiency to be "good enough"?

- Isn't lower energy always better?

- What is a meaningful definition of an energy constraint?

**Note #1**: Can you try to answer these questions as a hardware expert?

**Note #2:** Notice that we also begin to introduce new terminology ... energy constraints

- Isn't lower energy always better?

- What is a meaningful definition of an energy constraint?

- What does it mean if we have violated energy constraints?

- How can I characterize a design to see if I meet an energy constraint or not?

- What are the most meaningful semantics we can assign to the idea of "meeting energy"?

**Note #1**: Can you try to answer these questions as a hardware expert?

**Note #2:** Notice that we also begin to introduce new terminology ... energy constraints

### One other thing that follows from automation

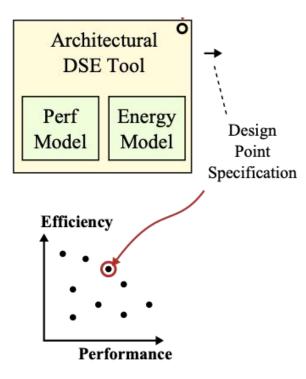

An automated approach requires an **explicitly defined energy model** (cost model)

- Previously we did *not* need good energy models!

- Simply bank on the chief architect's experience and intuition ...

### One other thing that follows from automation

An automated approach requires an **explicitly defined energy model** (cost model)

- Previously we did *not* need good energy models!

- Simply bank on the chief architect's experience and intuition ...

This is one of the key hurdles that faces an automated world

• The energy models that underlie future automation are very important

### One other thing that follows from automation

An automated approach requires an **explicitly defined energy model** (cost model)

- Previously we did *not* need good energy models!

- Simply bank on the chief architect's experience and intuition ...

This is one of the key hurdles that faces an automated world

- The energy models that underlie future automation are very important

- But these models can be *buggy*

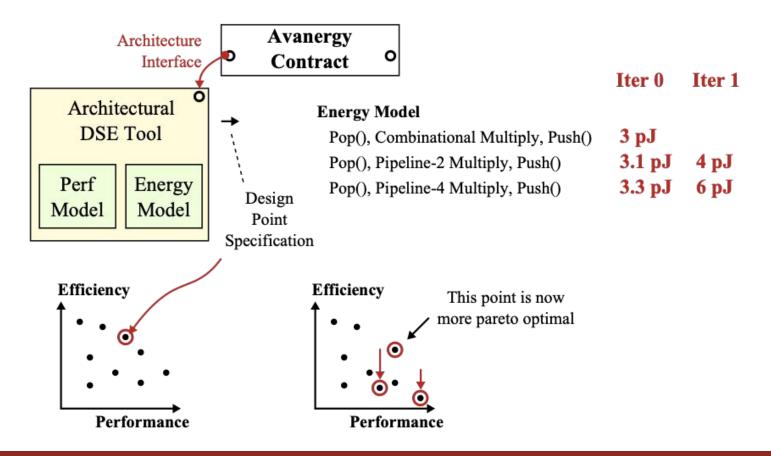

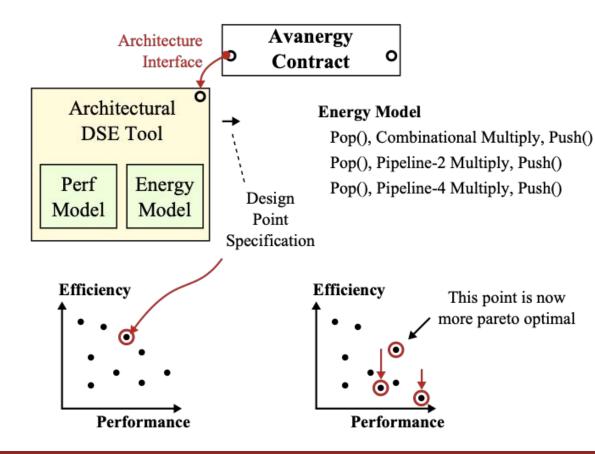

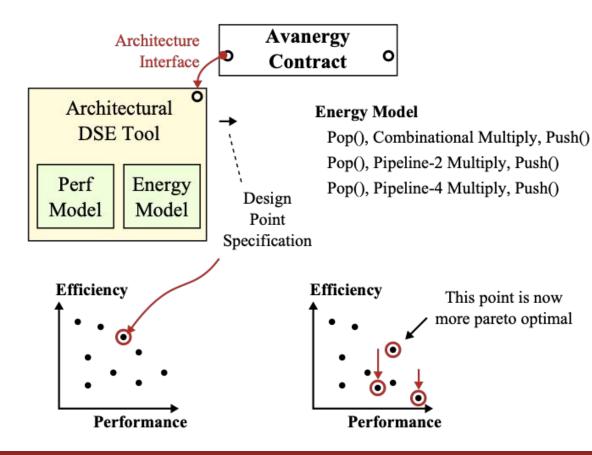

One of the key goals of this project is to solve this through iteration and a new abstraction

USC

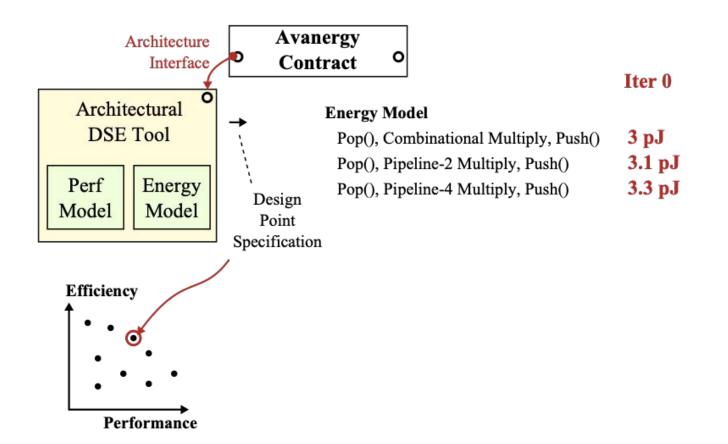

#### Iter 0 Iter 1

| 3 pJ   |      |

|--------|------|

| 3.1 pJ | 4 pJ |

| 3.3 pJ | 6 pJ |

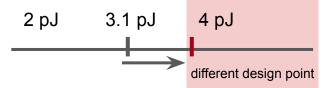

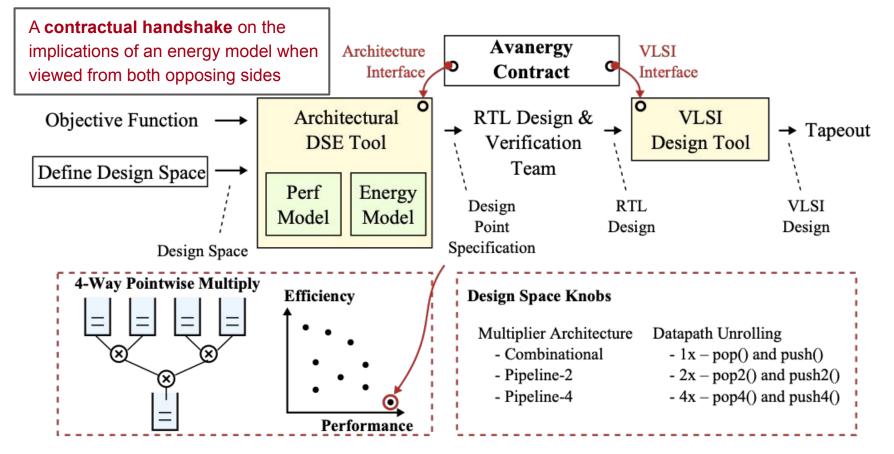

#### Goal of the architecture interface

Determine "how wrong" the transaction energy cost must be, where the DSE tool would have instead picked a different design point.

#### Iter 0 Iter 1

| 3 pJ   |      |

|--------|------|

| 3.1 pJ | 4 pJ |

| 3.3 pJ | 6 pJ |

#### Goal of the architecture interface

Determine "how wrong" the transaction energy cost must be, where the DSE tool would have instead picked a different design point.

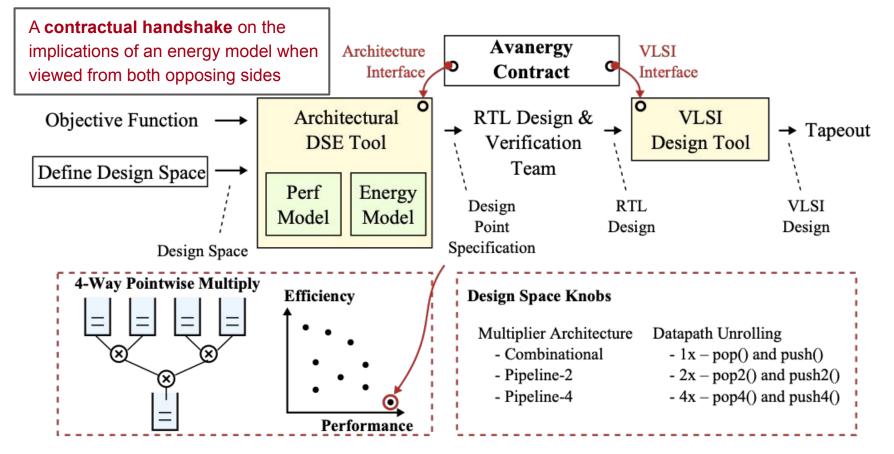

## The Avanergy Architecture Interface

### Iter 0 Iter 1

| 3 pJ   |      |

|--------|------|

| 3.1 pJ | 4 pJ |

| 3.3 pJ | 6 pJ |

#### Goal of the architecture interface

Determine "how wrong" the transaction energy cost must be, where the DSE tool would have instead picked a different design point.

## The Avanergy Architecture Interface

As a recipe:

- 1. Run many instances of the architectural design-space exploration tool with slightly perturbed values of the energy model

- 2. Run a relaxation algorithm to discover the most conservative values

- 3. Deliver energy constraints from these experiments for each entry in the energy model

As a recipe:

- 1. Run many instances of the architectural design-space exploration tool with slightly perturbed values of the energy model

- 2. Run a relaxation algorithm to discover the most conservative values

- 3. Deliver energy constraints from these experiments for each entry in the energy model

**Takeaway**: Energy constraints can be purposely constructed with semantics derived from the DSE tool (i.e., the requirements on the energy model to select this design point), and passed down for VLSI to confirm

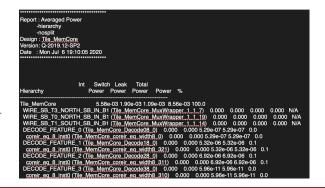

## The Avanergy VLSI Interface

#### Goal of the VLSI interface

Confirm that the energy constraints are met (this type of energy measurement is not a conventional step today)

## The Avanergy VLSI Interface

#### Goal of the VLSI interface

Confirm that the energy constraints are met (this type of energy measurement is not a conventional step today)

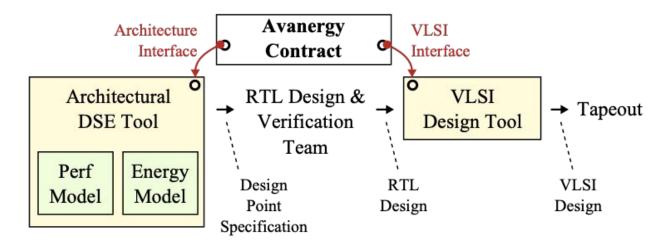

## Avanergy: An Architecture-VLSI Abstraction (Overview)

## **Brief Summary of Differences**

Implications for architectural design-space exploration framework designers

- In order for these tools to fit into a future of automated, iterative development, your tool must expect to be...

- Wrapped with an energy model that can be permuted

- Run many times to discover energy constraints for the first half of this contract

## **Brief Summary of Differences**

Implications for architectural design-space exploration framework designers

- In order for these tools to fit into a future of automated, iterative development, your tool must expect to be...

- Wrapped with an energy model that can be permuted

- Run many times to discover energy constraints for the first half of this contract

Implications for VLSI design team engineers

- There is a lack of support for characterizing "transactional" energy

- Future VLSI tools that support automated DSE should expect to establish some form of full-stack handshake

A new world of hardware designers may have (1) more people, (2) operating with less expertise, and (3) relying heavily on automated tools.

A new world of hardware designers may have (1) more people, (2) operating with less expertise, and (3) relying heavily on automated tools.

• Traditional design methodologies are based on the **wrong expertise profiles**

A new world of hardware designers may have (1) more people, (2) operating with less expertise, and (3) relying heavily on automated tools.

- Traditional design methodologies are based on the **wrong expertise profiles**

- A short and **agile iterative approach** can naturally accommodate error

A new world of hardware designers may have (1) more people, (2) operating with less expertise, and (3) relying heavily on automated tools.

- Traditional design methodologies are based on the **wrong expertise profiles**

- A short and agile iterative approach can naturally accommodate error

- Automation requires a systematic approach and **quantifiable abstractions**

A new world of hardware designers may have (1) more people, (2) operating with less expertise, and (3) relying heavily on automated tools.

- Traditional design methodologies are based on the **wrong expertise profiles**

- A short and agile iterative approach can naturally accommodate error

- Automation requires a systematic approach and **quantifiable abstractions**

**Avanergy** is a new abstraction that allows a quantitative and systematic view of the architecture-VLSI boundary to allow energy-aware design-space exploration in a way that future automated tools can build upon it.

## BACKUP